# Enhancement of PQ and integrate the solar power by DSTATCOM with variable DC Link voltage control

Gannerla Esha<sup>1</sup>, Vishnuvardhan Vadla<sup>2</sup>, Dr.P.Santosh Kumar Patra<sup>3</sup>

<sup>1</sup>Assistant Professor in Department of Electrical and Electronics Engineering <sup>2</sup>Assistant Professor in Department of Electrical and Electronics Engineering <sup>3</sup> Principal & Professor in Department of Computer science Engineering

St. Martin's Engineering College, Secunderabad, Telangana, India.

**ABSTRACT:** This paper proposes a novel control methodology for DC-link voltage of Distribution Static Compensator (DSTATCOM) in light of burden remuneration essential using Reduced Switch Count Multi-Level Converter (RSC-MLC) consolidated with Photo-Voltaic (PV) structure. The proposed system is prepared for amendment of reactive power, unbalance and frequency requested by three leg linear and non-linear loads related with the dispersion side, fast upgrading of intensity quality. It is also fit for giving authentic power sponsorship to the heap and right now source from getting over stacked at whatever point required. During off-top loads, the DC-interface voltage can be brought down to a lower regard, which will reduce the voltage-stress across switches of inverter and limits the trading disasters. The assortment of DC-link voltage is given using RSC-MLC which requires DC voltage supply. These methods use boundless resources of imperativeness, for instance, daylight based cells as the DC voltage source. The output voltage of PV exhibit is continue to a higher worth using High Gain Boost Converter (HGBC) and given to RSC-MLC. The maximum power point tracking (MPPT) of PV sheets is practiced by using Perturb and Observe (P and O) algorithm. The results have been checked through simulation considers.

**KEYWORDS:** Distribution Static Compensator (DSTATCOM), Reduced Switch Count Multi-Level

Converter (RSC-MLC), High Gain Boost Converter (HGBC), maximum power point tracking (MPPT). **I.INTRODUCTION:** The expansion of non-linear, inductive and uneven loads in the distribution framework has instigated two or three power quality issues [1]. It is a consequence of snappy move in the utilization of delicate mechanical assembly in current, business, close by and balance applications, for example, switched mode power supplies, PCs, fridges, TVs, and so on. The use side sales controlled load of power which fuses the use of intensity electronic converters. The generators produce a sinusoidal voltage in any case the streams drawn by such loads are wound and unequal. This effects the feeder voltage and prompts isolating of different loads related with a near feeder. Several custom power contraptions (CPD) have been utilized to beat these issues [2], [3]. Out of these CPD. Distribution Static Compensator (DSTATCOM) are extensively utilized for calming the current-based power quality issues which solidify poor force factor, conflicting streams and expanded impartial current. A couple DSTATCOM topologies and their plan have been shrouded in existing creating subject to the fundamental. Some customary methodology is 4-leg DSTATCOM and split-capacitor DSTATCOM [4], [5]. The 4-leg DSTATCOM topology utilizes one additional leg to give the best way to deal with fair current. This joins the utilization of additional progressions inciting the entire all the all the more exchanging

calamities. Split capacitor DSTATCOM experiences capacitive voltage unbalance issue as a result of conflicting charging of two capacitors at DC-interface. Right now, leg Voltage Source Inverter (VSI) topology with unbiased capacitor has been utilized, which conquers these issues [6].

It uses only one capacitor at the dc-link, so there is no capacitor voltage unbalance. Also, there is no need to introduce an extra leg with two more switches because the neutral current compensation is taken care by the small rated neutral capacitor. However, in most of the mentioned topologies, the dc-link voltage is kept constant based on rated load conditions [7]. This leads to unnecessary switching losses at reduced loads. The dc-link voltage can be reduced at reduced loads for minimization of switching losses associated with Voltage Source Inverter (VSI) without affecting compensation. In [8], adaptive dclink voltage variation has been proposed using PI controller. However, it suffers from slow transient response due to the behavior of PI controller and leads to rippled dc-link voltage which makes it unreliable for fast changing loads. In the proposed method, the dc-link voltage regulation is achieved using Reduced Switch Count Multi Level Converter (RSC-MLC). The gate pulses of inverter switches are controlled using Hysteresis Controller which is faster and simpler [9]. The gate pulses are derived using Instantaneous Symmetrical Component Theory (ISCT) to get the reference harmonic currents based on load demand [10]. These harmonic currents are used to find the required reference dc-link voltage. The RSC-MLC is operated using Pulse Width Modulation (PWM) technique to obtain the desired level of dc-link voltage. The specialty of this RSC-MLC topology is reduced voltage stress at any operating condition across switches, which leads to reduction in switching losses. Due to growing consumption of conventional sources of energy, there is a huge need to employ non-conventional resources in as many applications possible because they are freely available as well as non-polluting [11]. The solar energy is viewed as one of the popular and potential energy source for meeting the demands. The solar

## ISSN NO:2231-3990

energy is converted into electrical energy by using Photo Voltaic (PV) cells. Several analysis upon the stability and performance of the PV integrated systems for various applications have been performed [12], [13], [14]. In the proposed method, the PV panels are used to charge the batteries of RSC-MLC. The Maximum Power Point Tracking (MPPT) is achieved using Perturb & Observe (P & O) algorithm and the output voltage of PV panel is stepped up using High Gain Boost Converter (HGBC) [15]. During day time, PV panels produce maximum real power. Therefore, the batteries can be charged and real power support can also be provided. At night, PV panels cannot deliver real power due to insufficient irradiation. In this case, the batteries will support the dc-link voltage for reactive power and harmonic compensation. The real power can be shared intelligently based upon the availability of irradiation and demand. The complete details of dc-link voltage variation using proposed RSC-MLC for achieving power quality improvement and injection of real power is discussed below extensively.

#### **II.LITARATURE SURVEY:**

## 1) Implementation of Four-leg Distribution Static Compensator:

An execution of a four-leg distribution static compensator (DSTATCOM) utilizing a versatile neural system based control calculation for correction of linear/non-linear loads utilizing voltage source converter is exhibited here. The proposed control algorithm, which depends on versatile neural system, is utilized for extraction of basic active and reactive power segments of error currents which are significant parts in the estimation of reference supply currents. This control calculation is actualized on a created four-leg DSTATCOM for reactive power compensation, harmonics disposal, and load adjusting and nonpartisan current alleviation under linear and non-linear loads. The presentation of DSTATCOM is watched very agreeable under different linear and non-linear loads.

2) Three-leg inverter-based distribution static compensator topology for compensating unbalanced and non-linear loads:

This investigation proposes another three-leg voltage source inverter (VSI) - based distribution static compensator (DSTATCOM) topology to compensation lopsided and non-straight loads in low-voltage three-stage four-wire distribution frameworks. The proposed topology utilizes a threeleg VSI with a solitary DC link capacitor. This plan has an extra little AC capacitor which is associated between negative DC-bus to the framework nonpartisan. As the proposed topology utilizes a solitary DC-interface capacitor, the DC voltage offsetting issues related with the mainstream split capacitor impartial clasped VSI topology is kept away from. Additionally, the topology can remunerate impartial current without utilizing fourtopology. Examination leg inverter and demonstrating of the proposed topology is clarified in detail. Simulation considers are completed to check the presentation of the proposed plan and results are exhibited. The exhibition of the new topology has been contrasted and ordinary three-leg two level split capacitor VSI-based DSTATCOM topology. Results are additionally tentatively checked on a MATLAB facility model of DSTATCOM.

3) T-connected transformer integrated three-leg VSC based 3P4W DSTATCOM for power quality improvement

This paper gives power factor adjustment, harmonics compensation, load adjusting and nonpartisan current compensation of linear and nonlinear, variable and unequal loads utilizing custom power devices DSTATCOM for three-stage fourwire (3P4W) framework. Flawless Harmonic crossing out (PHC) hypothesis has been utilized for reference current generation. A three-leg voltage source converter topology with T-associated transformer as appropriation static compensator (DSTATCOM) is utilized right now. T-associated transformer is presented here for impartial current correction. Ability of this proposed scheme is exhibited utilizing results acquired from MATLAB-Simulink based condition.

#### **III.PROPOSED METHOD**

#### Proposed Operation Of Dstatcom Using RSC-MLC Integrated With Pv-Panels.

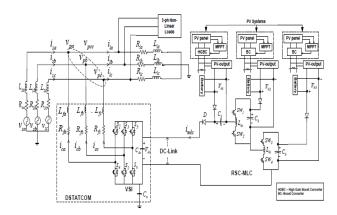

The schematic diagram of DSTATCOM for power quality improvement and PV energy injection with RSC-MLC on DC side of VSI is shown in Fig. 1. In maximum of the existing topologies of VSI, the DC-link voltage is maintained steady (i.e.: two times the peak of Vpcc) for all load conditions [7]. But, in truth the DC-link voltage required is low when gadget is operated at off-peak load situations. Therefore, regular rated DC-link voltage results in unwanted switching losses at some stage in reduced load situations. The DC-link voltage may be reduced at off-peak loads without compromising the compensation. This reduces the voltage stress throughout switches of VSI and minimizes the switching losses at reduced hundreds.

Fig. 1: RSC-MLC controlled DSTATCOM for PQ improvement and real power injection from PV in distribution system.

In the proposed approach, RSC-MLC is used for regulating the DC-link voltage of DSTATCOM. At reduced masses, it reduces the DC-link voltage which ends up in minimization of switching losses. The operation of RSC-MLC and selection of DC-link voltage based totally on numerous load necessities is explained right here in element. The DC-voltage assets used for RSC-MLC are PV-Panels that are a source of real electricity. Hence, the real strength sharing can also be finished

Volume IX, Issue V, May/2020

#### ISSN NO:2231-3990

### Alochana Chakra Journal

based totally on availability of sunlight and the load call for. The reference DC-link voltage for the proposed approach is estimated as shown.

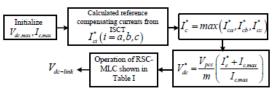

Fig. 2: Flow-chart for reference DC-link voltage calculation.

In Fig. 2 [8]. In Fig. 2, Ic;max is most compensating present day compensated with the aid of DSTATCOM for a given rated load condition. The reference rms compensating currents (Ici)are derived from the instant reference compensating currents received the use of ISCT [16], as given in (1).

$$i_{ck}^{*} = i_{lk} - \left(\frac{v_{sk}}{\sum_{j=a,b,c} v_{sj}^{2}}\right) P_{l}$$

(1)

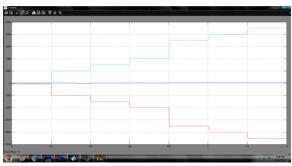

Where, K = a, b and c levels. Vsk is deliver segment voltages, ilk is load currents, ick represents the reference compensating currents and Pl is the common real energy demanded via the load. However, the very last DC-link voltage (Vdc) is chosen based totally on the ranges of reference DC voltage (V \_dc) the use of RSC MLC. The maximum DC-link voltage (Vdc;max) within the proposed technique is taken into consideration as twice of one.6 times peak of PCC voltage [6]. The DC-hyperlink voltage and corresponding switches operated in RSC-MLC are proven in Table. I.

TABLE I: DC-link voltages corresponding to switching devices of RSC-MLC

| Ranges of $V_{dc}^*$           | Operating switches in RSC-MLC          | DC-link voltage                                          |

|--------------------------------|----------------------------------------|----------------------------------------------------------|

| $< V_{dc,min}$                 | $sw_2, sw_4$                           | $V_{b1}$                                                 |

| $V_{dc,min} - V_1$ $V_1 - V_2$ | $sw_1(d_1), sw_4$<br>$sw_1(d_2), sw_4$ | $V_{b1}+V_{b2}*d_1$<br>$V_{b1}+V_{b2}*d_2$               |

| $V_{2} - V_{3}$                | $sw_1, sw_4$                           | $V_{b1}+V_{b2}$                                          |

| $V_3 - V_4 V_4 - V_5$          | $sw_1, sw_3(d_1)$<br>$sw_1, sw_3(d_2)$ | $V_{b1}+V_{b2}+V_{b3}*d_1$<br>$V_{b1}+V_{b2}+V_{b3}*d_2$ |

| $V_5 - V_{dc,max}$             | $sw_1, sw_3$                           | $V_{b1} + V_{b2} + V_{b3}$                               |

The DC-link voltage levels is divided similarly in steps from VDC; min to Vdc;max. The voltage range from Vdc;min to Vdc;max is divided such that with every next operation of transfer, the subsequent increment in voltage step (\_Vdc) is obtained.

$$\Delta V_{dc} = \frac{V_{dc,max} - V_{dc,min}}{6} \tag{2}$$

Hence the voltage varies in steps consisting of Vdc;min, (Vdc;min +Vdc), (Vdc;min + 2 Vdc), ...., Vdc;max, primarily based at the calculated V DC cost similar to load. The RSC-MLC is largely a kind of dollar-converter which steps down the input DC voltage by using the aspect of duty-cycle. To get the desired voltages, the switches of RSC-MLC are operated with certain duty cycles. Here, the obligation cycle d1 = 1=three and d2 = 2=three are selected to obtain the equal voltage division between Vdc;min to Vdc;max by means of getting the desired increment Vdc within the DC hyperlink voltage. Here, Vdc;min is identical as the voltage throughout battery(Vb1) and Vdc;max = Vb1+Vb2+Vb3. By choice of such obligation cycles, the fee of dc-link voltage is shown in TableI. For instance: (a) Vdc;min = Vb1 received by way of switching ON sw2 and sw4 completely, (b) Vdc; min+ Vdc = Vb1+Vb2 d1and Vdc;min + 2 Vdc =Vb1 + Vb2 \_ d2 are acquired by keeping sw4 ON and operating sw1 with responsibility cycles d1 andd2, respectively. In the same way, to get Vdc;max, sw1 andsw3 are switched ON completely.

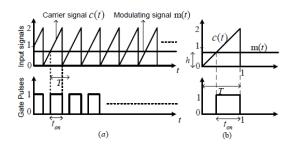

Fig. 3: Generation of gate pulses from carrier signal and modulating signal.

The duty cycles d1 and d2 are obtained and gate pulses are generated for the switches sw1 to sw4 using noticed tooth-step PWM technique as proven in Fig. 3(a). The gate pulses are generated by comparing service sign (c(t)) and modulating signal (m(t)). If c(t) > m(t), gate pulse is common sense one (i:e:;ON duration (ton), in any other case logic zero (i:e:; OFF length). By varying the significance of modulating sign, the ton period can be numerous,

which is explained beneath. From similarity of the triangles of the discern proven in Fig. Three(b), the following relation may be written,

$$\frac{h}{T - t_{on}} = \frac{2}{T} \tag{3}$$

Where, T is general term of pulse, h be the magnitude of modulating signal. The expression of obligation cycle d for operation of switches can be given as d = ton=T. By various the frequency of provider signal, each the ton and T changes, such that the duty cycle remains same. Therefore, for simplicity in calculation, the time-length T is scaled down to 1 (i.e. T = 1). For obligation cycle d1 = 1=3, ton = 1=three, the calculated price from (three) is h = 4=3. Similarly, for duty cycled 2 = 2=3, ton = 2=3, h = 2=three is acquired. Therefore the modulating indicators of value h =four=three and h= 2=three is used to get d1 = 1=3 and d2 = 2=3respectively. By operating the switches of RSC-MLC with these responsibility cycles, the output voltage stages can be varied in identical steps with improved flexibility. Hence, at decreased hundreds, the switching losses in VSI are minimized due to decreased DC-link voltage. Here, 7 DC voltage levels have been carried out using the RSCMLC shown given in Fig. I.A. Designing of RSC-MLC Parameters Design of DC-link inductor (Ldc): The right design of DC hyperlink inductor is important so that it will do away with the current ripples and lets in to obtain the voltage versions in smooth manner. The RSC-MLC is essentially running as DC-DC greenback converter with changed functions. Let, fsw =switching frequency, \_IL;max =maximum modern ripple via inductor, Ldc =DClink inductance. Then, from the primary equations of dollar converter, following equation is obtained [17].

$$\Delta I_{L,max} = \frac{V_{b2} \quad (or) \quad V_{b3}}{4L_{dc} f_{sw}} \tag{4}$$

The inductor, Ldc is designed based totally on \_IL;max. In this paper,Vb2 = 200 V, fsw = 10 kHz, \_IL;max = 0:1 A. After substituting a lot of these values, the price of Ldc = 50 mH. Design of capacitors: The DC-link capacitor performs a major role in disposing of the voltage ripples and maintaining the output voltage of RSC-MLC. Since, Volume IX, Issue V, May/2020

the RSC-MLC is using DC-voltage resources in the shape of PV panels, the ripple in the voltage is already very less. Hence the rating of the capacitor is very much less. Let, \_Vo;max be the maximum voltage ripple across DC-link capacitor and Cdc is DC-link capacitance. Then from the dollar converter primary equations [17],

$$\Delta V_{o,max} = \frac{V_{dc}}{32L_{dc}C_{dc}f_{sw}^2} \tag{5}$$

For higher overall performance, the allowable ripple voltage is considered as 3% of Vdc. By substituting the values in (5), the obtained capacitor cost is, Cdc = zero.2 \_F. The capacitors C1, C2 and C3 proven in Fig. 1 are connected in parallel to the PV panels. They assist in putting off the voltage ripples on the output of PV panel, and also used for charging the batteries linked in parallel to them. The design of those capacitors rely on the voltage score and current through them. Their values are predicted using following expressions, q=CVC wherein q is charge and VC is rated voltage across capacitor having capacitance C. So,

$$I_C = \frac{C\Delta V_C}{\Delta t} \tag{6}$$

Where IC= present day via C,  $\_VC=$  height to top ripple voltage throughout C,  $\_t = 1=$ fsw. Substituting and rearranging the terms, following expression is obtained.

$$C = \frac{I_C}{f_{sw}\Delta V_C} \tag{7}$$

Here, the capacitors C1, C2 and C3 are linked across PV panels of rated output voltage (VC) 700 V, 2 hundred V and200 V respectively. Here, \_VC=3% of VC, IC= zero.5 A as maximum allowable modern thru capacitors and fsw=10kHz are taken into consideration. Substituting those values, the values of capacitors, C1=2.38 \_F, C2=eight.33 \_F and C3=8.33 \_F are obtained.

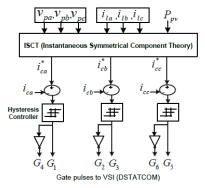

#### **B.** Generation of Gate Pulses for DSTATCOM.

The proposed algorithm of gate pulses era for DSTATCOM is exposed in Fig. 4. The estimate compensating currents are resulting utilizing ISCT [16]. These estimated compensating currents are in evaluation with measured compensating currents supplied via DSTATCOM and errors are given to

hysteresis controller. It generates gate pulses, so one can activate the DSTATCOM in this type of way that it injects accurately the same compensating contemporary required by way of the load.

Fig. 4: Control algorithm of gate pulse generation for DSTATCOM.

Hence, the DSTATCOM is capable of compensate the harmonic current and reactive power demanded via the weight and also supplies the actual energy generated from PV machine. Therefore, source present day turns into loose from harmonics and materials only real strength, enhancing the supply power element.

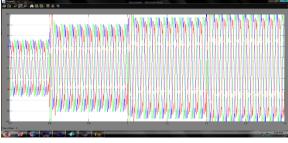

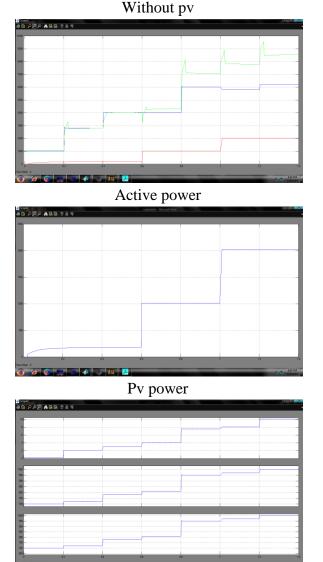

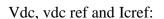

#### **IV.SIMULATION RESULTS:** Without PV and with PV:

0.1-0.7:

Ic without pv

Isabc without pv

Ic without pv

ISSN NO:2231-3990

Volume IX, Issue V, May/2020

## **V.CONCLUSION**

A new approach is proposed to modify the DC-link voltage using RSC-MLC without affecting the performance of DSTATCOM. It also uses renewable power sources for acquiring DC voltage source such as PV panels, Fuel cells. Using PV panels efficiently permits it to deliver real energy in addition to compensation to the burden at some stage in day time and paintings simply as DSTATCOM for energy great development at night time. It can be determined from simulation that compensation for reactive consequences strength and harmonics has been performed effectively. The supply modern is balanced, sinusoidal, distortion-loose and with stepped forward power issue. The %THD has reduced substantially after compensation. Also, due to Volume IX, Issue V, May/2020

## ISSN NO:2231-3990

reduced dc-link voltage at lesser hundreds, voltage strain throughout the switches has reduced and switching losses are minimized to an awesome volume, increasing the lifetime and efficiency of DSTATCOM. Hence, it could be an awesome alternative for power first-class improvement and real power aid to the load.

#### **REFERENCES:**

#### REFERENCES

[1] J. Arrillaga, N. R. Watson, "Power system harmonics," John Wiley and Sons, 2004.

[2] A. Ghosh A, G. Ledwich, "Power Quality Enhancement using CustomPower Devices," Springer Science and Business Media, 2012.

[3] M. H. J. Bollen, "Understanding Power Quality Problems: Voltage Sagsand Interruptions," Wiley -IEEE press, Piscataway, NJ, USA, 2002.

[4] B. Singh, S. R. Arya, C. Jain, S. Goel, "Implementation of Four-legDistribution Static Compensator," IET Gener. Transm. Distrib., vol. 8,no. 6, pp. 1127-1139, June 2014.

[5] R. P. Tondare, S. P. Gawande, M. R. Ramteke, "Modeling of SplitCapacitor Based DSTATCOM and Voltage Balancing Scheme for LoadCompensation," International Conference on Emerging Trends in Communication, Control, Signal Processing and Computing Applications(C2SPCA), Bangalore, pp. 1-6, 2013.

[6] M. V. Manoj Kumar, M. K. Mishra, "Three-leg Inverter-based DistributionStatic Compensator Topology for Compensating Unbalanced and NonlinearLoads,"IET Power Electron., vol. 8, no. 11, pp. 2076-2084, Nov.

2015.

[7] B. Singh, P. Jayaprakash, D. Kothari, "A T-Connected Transformer andThree-leg VSC Based DSTATCOM for Power Quality Improvement,"IEEE Trans. Power Electron., vol. 23, no. 6, pp. 2710-2718, Nov. 2008.

[8] M. Hareesh, G. Siva Kumar, D. Sreenivasarao, "Dynamic DC VoltageRegulation of Split-Capacitor DSTATCOM for Power Quality Improvement,"IET Gener. Transm. Distrib., vol. 11, no. 17, pp. 4373-4383, Dec.2017.

.

[9] M. K. Mishra, K. Karthikeyan, "An Investigation on Design and SwitchingDynamics of a Voltage Source Inverter to Compensate Unbalancedand Nonlinear Loads," IEEE Trans. Ind. Electron., vol. 56, no. 8, pp.2802-2810, Aug. 2009. ISSN NO:2231-3990

[10] B. Singh, A. Chandra, K. Al-Haddad, "Power quality: problems andmitigation techniques," John Wiley & Sons Ltd., United Kingdom, Dec. 2014.